오늘은 ALU가 수행하는 기본적인 연산 중 하나인 시프트연산과 그 종류에 대해서 알아보겠습니다.

1. 논리적 시프트

논리적 시프트 연산이란 레지스터 내의 데이터 비트들을 왼쪽 혹은 오른쪽으로 한 칸씩 이동시키는 것을 말합니다.

예시를 보겠습니다.

위의 그림은 좌측-시프트연산(shift-left) 수행을 보여주고 있습니다.

비트들을 왼쪽으로 한 칸씩 이동하고, 맨 우측 비트로는 0이 들어오는것을 확인할 수 있습니다.

0100 비트에 좌측-시프트 연산을 수행하면 1000이 되어 2를 곱한 결과가 됩니다.

반대 방향인 우측-시프트(shift-right) 연산에서는 최상위 비트에 0이 들어오고, 모든 비트들이 우측으로 한칸씩 이동합니다.

최하위 비트는 버리게 됩니다. 이 경우에는 0100이 0010이 되어 원래의 수를 2로 나눈 값이 됩니다.

이처럼 시프트는 간단한 곱셈과 나눗셈에도 사용될 수 있습니다.

논리적 시프트 연산: 레지스터 내의 데이터 비트들을 왼쪽 혹은 오른쪽으로 한 칸씩 이동하는 연산

4-비트 레지스터는 네 개의 플립-플롭들로 구성되므로, 각 플립-플롭의 출력이 왼편 혹은 오른편의 플립-플롭으로 입력된다는 것을 의미합니다.

위의 그림은 D 플립-플롭을 이용한 시프트 레지스터의 내부 구성도를 보여주고 있습니다.

좌측 시프트를 원하는 경우에는 제어 신호 L을 1로 세트하면, 그 신호가 접속된 AND게이트들의 한쪽 입력이 1로 세트되어서,

각 플립-플롭은 우측 플립-플롭의 출력을 D 입력으로 받을 수 있게 됩니다. 맨 우측 AND 게이트로는 0이 입력됩니다.

입력되는 값들은 클록신호가 들어오는 순간에 각 플립-플롭에 저장됩니다.

플립-플롭: 1비트 정보를 저장할 수 있는 기억장치 논리회로

시프트 레지스터(shift register): 데이터 비트들을 좌측 혹은 우측 방향으로 이동시키는 기능을 가지고 있는 레지스터

2. 순환 시프트

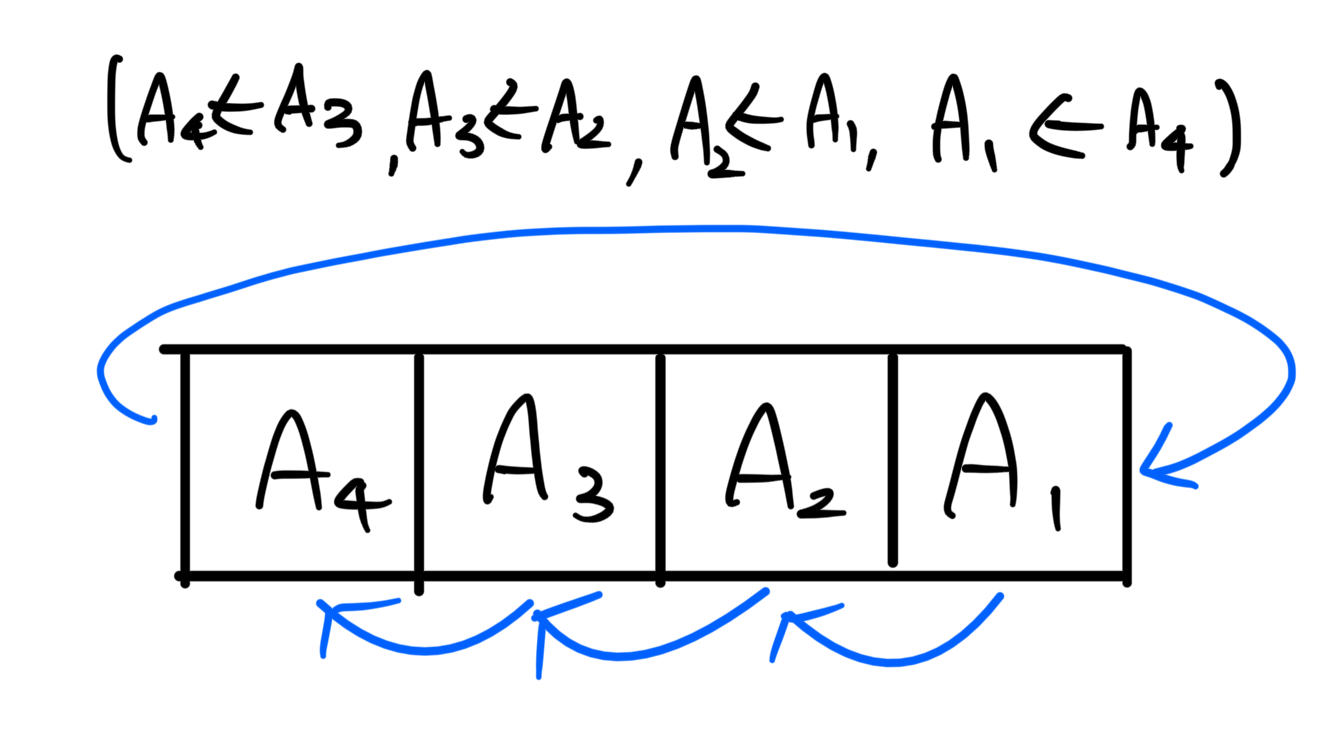

회전이라고도 부르는 순환 시프트 연산은 최상위 혹은 최하위 비트를 버리지 않고 반대편 끝에 있는 비트 위치로 들어가게합니다.

순환 좌측-시프트 연산을 보면 최상위 비트인 A4가 최하위 비트인 A1의 위치로 들어갑니다.

차이를 보면 다음과 같습니다.

A= 1 0 1 1

-> 0 1 1 0 (좌측-시프트 연산)

-> 0 1 1 1 (순환 좌측-시프트 연산)

순환 우측-시프트 연산의 경우에는 비트들 간의 이동이 A4 -> A3, A3 -> A2, A2 -> A1, A1 -> A4와 같이 이루어집니다.

시프트 연산을 데이터 수만큼 연속적으로 수행함으로써 두 레지스터들 사이에 한 개의 선을 통하여 전체 데이터를 이동하는 직렬 데이터 전송이 가능해집니다.

직렬 데이터 전송은 병렬 데이터 전송과 비교했을때 필요한 배선/선로의 수가 적고, 장거리 전송에 적합하다는 장점이 있습니다.

예시로 A 레지스터의 내용을 B 레지스터로 직렬 전송 하는 경우를 살펴보겠습니다.

직렬 전송에서는 각 클록 주기마다 한 번씩의 시프트 연산이 일어납니다.

따라서 4-비트 레지스터들 간의 직렬 전송에서는 A레지스터에서 네번의 순환시프트연산이 수행되고 B레지스터에서는 네 번의 논리적 시프트가 수행되어야 합니다.

위의 표에서는 A가 1011인 A레지스터에서 B레지스터로 직렬 데이터 전송을 하는 모습을 보여주고 있습니다.

순환 시프트(circular shift): 좌측 혹은 우측 시프트 후에 최상위 혹은 최하위 비트를 버리지 않고 반대편 끝으로 이동시키는 시프트 연산

직렬 데이터 전송(serial data transfer): 두 레지스터들 간에 접속된 하나의 선을 통하여 데이터를 한 번에 한 비트씩 전송하는 동작

3. 산술적 시프트

산술적 시프트 연산은 레지스터에 저장된 데이터가 부호를 가진 정수인 경우에 부호 비트를 고려하여 수행되는 시프트 연산입니다.

예를 들어, 2의 보수로 표현된 4-비트 데이터에서 맨 좌측 비트(A4)가 부호 비트인 경우에 산술적 시프트는 다음과 같이 이루어집니다.

산술적 좌측-시프트: A4(불변), A3 <- A2, A2 <- A1, A1 <- 0

산술적 우측-시프트: A4(불변), A4 -> A3, A3 -> A2, A2 -> A1

산술적 우측-시프트는 이전 포스팅에서 다뤘던 부호-비트확장과 같은 결과를 가집니다.

[컴퓨터 구조] 산술논리연산장치(ALU)의 구성요소와 정수의 표현

오늘은 산술논리연산장치의 구성요소를 간략하게 알아보고 연산에 사용되는 정수들이 어떤식으로 표현되는지를 알아보겠습니다.1. 산술논리연산장치(ALU)1) 산술논리연산장치(ALU) 개요산술논리

5g-0.tistory.com

산술적 시프트(arithmetic shift): 부호를 가진 데이터에 대한 시프트 동작, 부호 비트는 변경되지 않음

부호-비트 확장(sign-bit extension): 2의 보수를 더 긴 단어로 확장할 떄 부호 비트를 상위 비트들로 복제하는 동작

-2에 대한 산술적 우측-시프트 연산을 연속적으로 수행한 결과를 예시로 보겠습니다.

A = 1 1 1 0 (-2)

1 1 0 0 (-4) 산술적 좌측-시프트

1 1 1 0 (-2) 산술적 우측-시프트

1 1 1 1 (-1) 산술적 우측-시프트

4. C 플래그를 포함한 시프트 연산

1) C플래그를 포함한 시프트 연산

시프트 연산 시 Carry플래그는 밀려나간 비트를 임시로 저장하는 용도로 쓰입니다.

실제 CPU에서는 일반적으로 시프트 연산에 올림수(C)플래그가 포함됩니다.

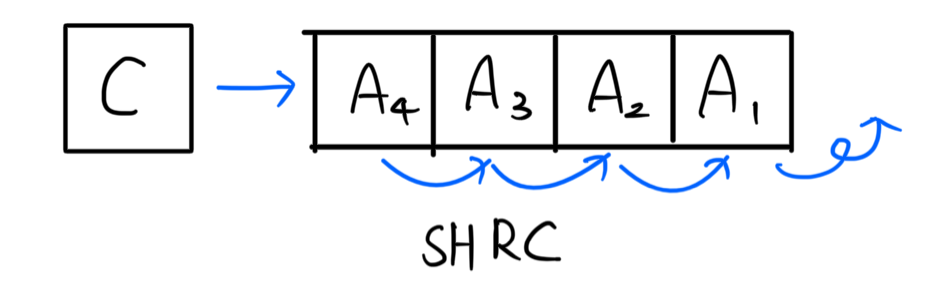

먼저 C 플래그를 포함한 좌측-시프트(SHLC: shift left with carry) 입니다.

최상위 비트인 A4가 버려지지 않고 C 플래그로 이동합니다. 이때 원래의 C 플래그 값은 지워집니다.

C 플래그를 포함한 우측-시프트(SHRC: shift right with carry) 에서는 C 플래그의 값이 A4로 이동하고 A1비트는 버립니다.

2) C 플래그를 포함한 순환 시프트 연산

C 플래그를 포함하는 순환 시프트연산에서는 C 플래그로 데이터의 최상위 비트 혹은 최하위 비트의 값이 들어옵니다. 그리고 C 플래그의 원래 값은 지워지지 않고 최상위 혹은 최하위 비트로 이동합니다.

산술적 시프트 연산에서도 C플래그가 포함될 수도 있는데, 그러한 연산에서 비트들의 이동동작은 논리적 시프트 연산과 동일합니다.

산술적 우측 시프트 에서 C플래그의 값이 포함되는 경우에, 그 값이 원래의 부호 비트값과 다른 경우에는 데이터 부호가 변경되는 문제가 발생합니다. 이런 경우에는 오버플로(V)플래그를 세트함으로써 그 사실을 알리거나, C플래그가 레지스터로 들어오지 못하게 함으로써 부호 비트가 그대로 유지되게 합니다.

아이패드 업데이트 하고나서 그림그리는게 참 힘들어졌어요

굿노트가 버벅이네요 롤백을 해야하나;

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 부동소수점 수의 표현과 산술연산 (0) | 2025.04.22 |

|---|---|

| [컴퓨터 구조] 정수의 산술 연산 (2) | 2025.04.16 |

| [컴퓨터 구조] 논리연산 (0) | 2025.04.10 |

| [컴퓨터 구조] 산술논리연산장치(ALU)의 구성요소와 정수의 표현 (0) | 2025.04.09 |

| [컴퓨터 구조] 상용 프로세서들의 명령어 형식 (2) | 2025.04.08 |